Foundry

晶圆代工厂

Foundry是指仅专注于芯片制造的半导体公司。Foundry不设计芯片,只严格按客户的芯片设计版图完成芯片生产。

IDM

Integrated Device Manufacturer

整合器件制造商

IDM公司自主完成芯片设计、制造、封装、测试到销售的全流程,无需外包核心环节。

Wafer

晶圆

晶圆是芯片制造的基础载体,通常为硅片。现在常用的晶圆的规格有8英寸(约200mm)和12英寸(约300mm)。

Die

裸片

晶圆在完成所有电路制造工艺后,会被切割成一个个的小方块,每一个小方块就是一个Die,Die没有经过封装,不能正常使用。

Scribe Line

切割道

切割道是晶圆表面预留的、用于切割各个Die的“空白区域”。

切割道的主要功能:

物理分隔相邻的Die,避免切割时损伤其中的电路。

工艺标记和测试:切割道中一般包含对准标记、Test Key等,用于光刻等工艺的定位校准和在制造过程中inline监控工艺质量和电性参数。

应力释放:减少切割时机械应力对die的影响,降低破片的风险。

Test Key

测试结构、测试键

Test Key是晶圆上专门设计的用于工艺验证和电性测试的器件或电路结构。一般将Test Key画在切割道内,包括不同尺寸的NMOS、PMOS、电阻、电容以及其他工艺相关的特性。

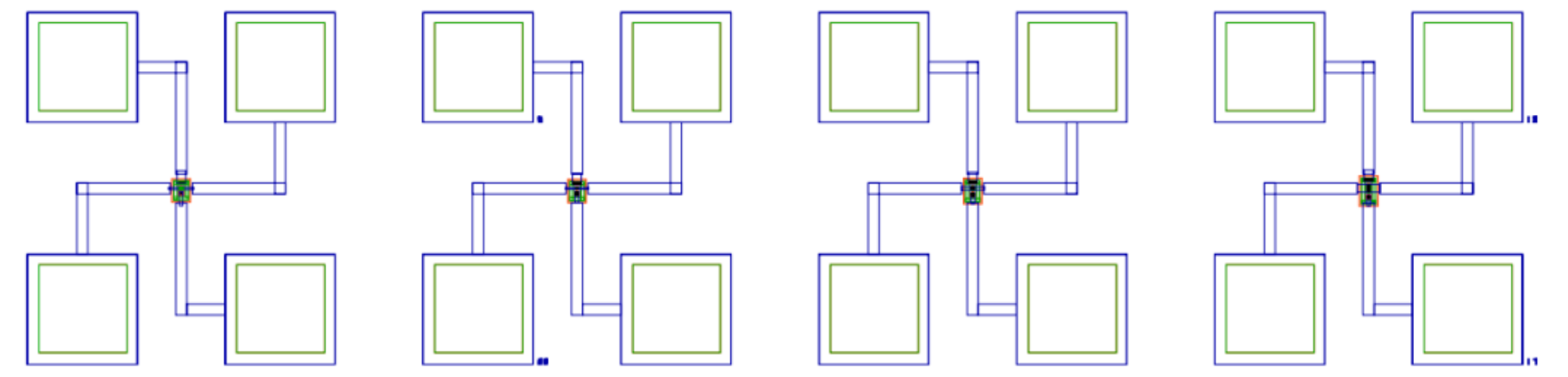

不同W/L比的NMOS测试结构

DFM

Design for Manufacture

可制造性设计

DFM是指在芯片设计阶段就充分考虑制造、封测等后续量产环节的工艺要求、生产约束、良率等影响因素。通过对芯片架构、版图、工艺选型的优化,让设计适配工艺,避免因设计问题导致制造困难或成本过高。

DTCO

Design Technology Co-Optimization

设计工艺协同优化

DTCO摒弃了传统的设计与工艺分离的研发模式,强调从芯片设计的最初阶段直到最终制造环节,设计团队与工艺团队紧密协作,同步优化设计架构、标准单元、器件结构和工艺参数,实现芯片性能、功耗、面积和成本(PPAC)最优的综合目标。

BJT

Bipolar Junction Transistor

双极结型晶体管

BJT是电子和空穴两种载流子参与导电的半导体三极管,三个电极分别为基极(B)、集电极(C)和发射极(E)。通过基极的小电流来控制集电极与发射极间的大电流,实现电流放大、开关控制的核心功能,是构成模拟电路、功率电路的基础器件。

FET

Field-Effect Transistor

场效应晶体管

场效应晶体管是一种通过电场效应来控制电流的半导体器件。其本质是通过外加电场改变半导体中载流子的分布,从而调节沟道的导电性,实现对电流的控制。

场效应晶体管有两种基本类型:结型场效应晶体管(JFET)和金属-氧化物-半导体场效应晶体管(MOSFET)。

CMOS

Complementary Metal-Oxide-Semiconductor

互补金属氧化物半导体

CMOS是在统一集成电路上NMOS和PMOS晶体管的混合,广泛应用于集成电路中。通过组合NMOS和PMOS,可以实现低功耗、高集成度的数字电路设计。

SOI

Silicon on Insulator

绝缘体上硅

SOI是一种半导体制造技术,其核心结构是在硅衬底与顶层硅之间加入一层绝缘体,形成“硅-绝缘体-硅”的三层结构。这种设计可以实现低功耗、高速度、抗干扰、抑制短沟道效应等技术优势。

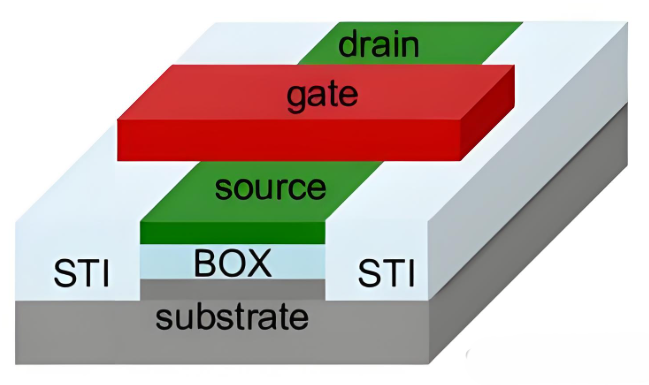

SOI器件结构

FinFET

鳍形场效应晶体管

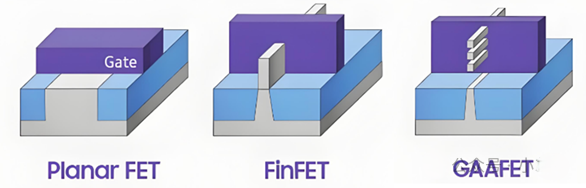

FinFET将传统平面MOSFET的二维结构改为垂直于衬底的鳍形结构。栅极从三面环绕沟道,从而显著抑制漏电流,缓解短沟道效应。FinFET主要应用于14nm到7nm的工艺制程。

GAA

Gate All Around

全环绕栅极场效应晶体管

将FinFET的鳍形栅进一步细化为水平放置的纳米线或纳米片,栅极完全环绕沟道,可以几乎消除短沟道效应。GAAFET主要应用于3nm及以下的工艺制程。

平面晶体管、FinFET、GAA晶体管结构

FEOL

Front-End-of-Line

前道工艺

FEOL是在硅晶圆衬底上制造晶体管及基本元件的一系列工艺步骤,是芯片制造的 “核心电路构建阶段”。 所以前道工艺直接决定晶体管的尺寸、性能和集成密度。

BEOL

Back-End-of-Line

后道工艺

BEOL在FEOL制造的晶体管基础上,进行金属互联,实现元件间电信号传输的工艺步骤,是芯片 “功能互联与封装的前置阶段”。

OPC

Optical Proximity Correction

光学邻近校正

OPC是一种光刻增强技术,用于补偿光刻过程中因光学衍射和干涉导致的图案失真,确保芯片制造的精度。通过计算机模拟光刻过程,预测图案失真,然后对掩膜版图案进行反向补偿。例如,在直角处添加辅助尖角、调整线条宽度来补偿线宽变化。

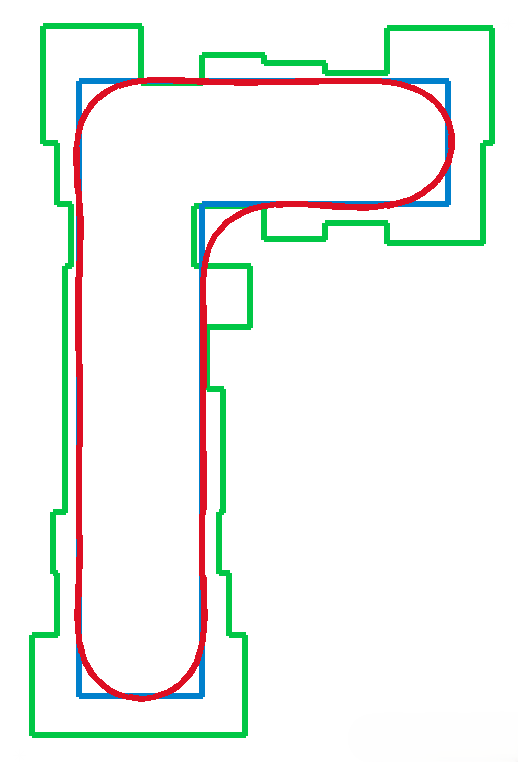

OPC后,光刻图形得到补偿

LITHO

Lithography

光刻

光刻是半导体制造中最核心的工艺步骤。通过光刻,将掩膜版上的电路图案,精准转移到晶圆表面的光刻胶上,再经过显影、刻蚀等步骤,在晶圆上形成微纳米级的电路图案。

PR

Photo Resist

光刻胶

光刻胶是一种对特定波长光线敏感的光敏高分子聚合物。光刻胶旋涂在晶圆表面后,会在光刻机的光照下发生光化学反应,实现曝光区域与未曝光区域的溶解性差异,从而将掩膜版上的电路图案精准复刻在晶圆表面。

PVD

Physical Vapor Deposition

物理气相沉积

PVD是半导体制造中用于薄膜沉积的一种工艺,通过溅射、蒸发、离子束等物理方式,打破靶材的原子间结合力,将固态靶材变成气相粒子。气相粒子在真空腔体内无规则运动,向晶圆表面扩散,在接触到晶圆表面后,气相粒子失去动能并吸附、成核、生长,形成均匀、致密的薄膜。

CVD

Chemical Vapor Deposition

化学气相沉积

CVD是半导体制造中用于薄膜沉积的一种工艺,区别于PVD的纯物理过程,CVD通过气相化学反应让气态前驱体在高温、等离子体等条件下,在晶圆表面发生分解、化合,生成固态物质并沉积形成均匀薄膜。

CMP

Chemical Mechanical Polish

化学机械研磨

CMP通过化学腐蚀与机械研磨的协同作用,去除晶圆表面的凸起部分,使晶圆表面达到极高的平整度和光洁度。CMP是唯一能实现晶圆全局纳米级平坦化的技术。

ADI

After Develop Inspection

显影后检查

光刻显影后、刻蚀或离子注入前,需要进行ADI检查。这是光刻图案转移的第一道质量校验,针对晶圆表面光刻胶形成的图案进行高精度检测,确认光刻胶图案是否符合Spec要求。

AEI

After Etching Inspection

刻蚀后检查

刻蚀会直接决定电路图案的精度,所以在刻蚀完成后,需要进行ADI检查,检测刻蚀后电路图案的CD、线间距、侧壁垂直度等核心指标。

Local Oxidation of Silicon

硅局部氧化隔离

LOCOS是早期CMOS、BJT器件的核心隔离技术。通过光刻、刻蚀、热氧化,在硅片表面选择性生长SiO2,将芯片上的有源区相互隔离,防止器件之间的电信号串扰。

LOCOS工艺简单、成本低,但会产生鸟嘴效应,缩小实际有源区面积,而且集成度越高,鸟嘴效应的影响越显著。

STI

Shallow Trench Isolation

浅槽隔离

STI是现在主流的隔离工艺。通过在硅片上刻蚀浅沟槽,填充绝缘介质,再进行平坦化的方式实现有源区隔离。

RTA

Rapid Thermal Anneal

快速热退火

RTA利用高功率光源的辐射热,直接照射晶圆表面,使晶圆从室温快速升温至工艺所需温度,通常在600~1200℃,升温速率可达50~200℃/秒。

Q-Time

Queue Time

等待时间

在半导体制造过程中,wafer完成上一道工艺后,一般不会立即进入下一道工艺,而是在缓冲区或特定区域等待,这个等待时间叫做Q-Time。

TO

Tape Out

流片

Tape Out指将完成设计验证的芯片版图(GDSII)交付给代工厂制作光掩膜版,正式进入芯片制造阶段的过程。

Full Mask

全掩膜

半导体制造流程中,所有的掩膜版都专门用于生产同一款芯片。这种方式通常用于芯片设计完全、验证成功并准备进入大规模商用生产的阶段。生产效率高,但成本也非常高。

MPW

Multi-Project Wafer

多项目晶圆

MPW是将多个使用相同工艺的集成电路设计放在同一个wafer上流片。制造完成后,每个设计项目可以得到几十片到上百片的芯片样品。流片费用由所有参加MPW的项目按照芯片面积分摊,所以流片成本的很小,极大地降低了产品开发风险。

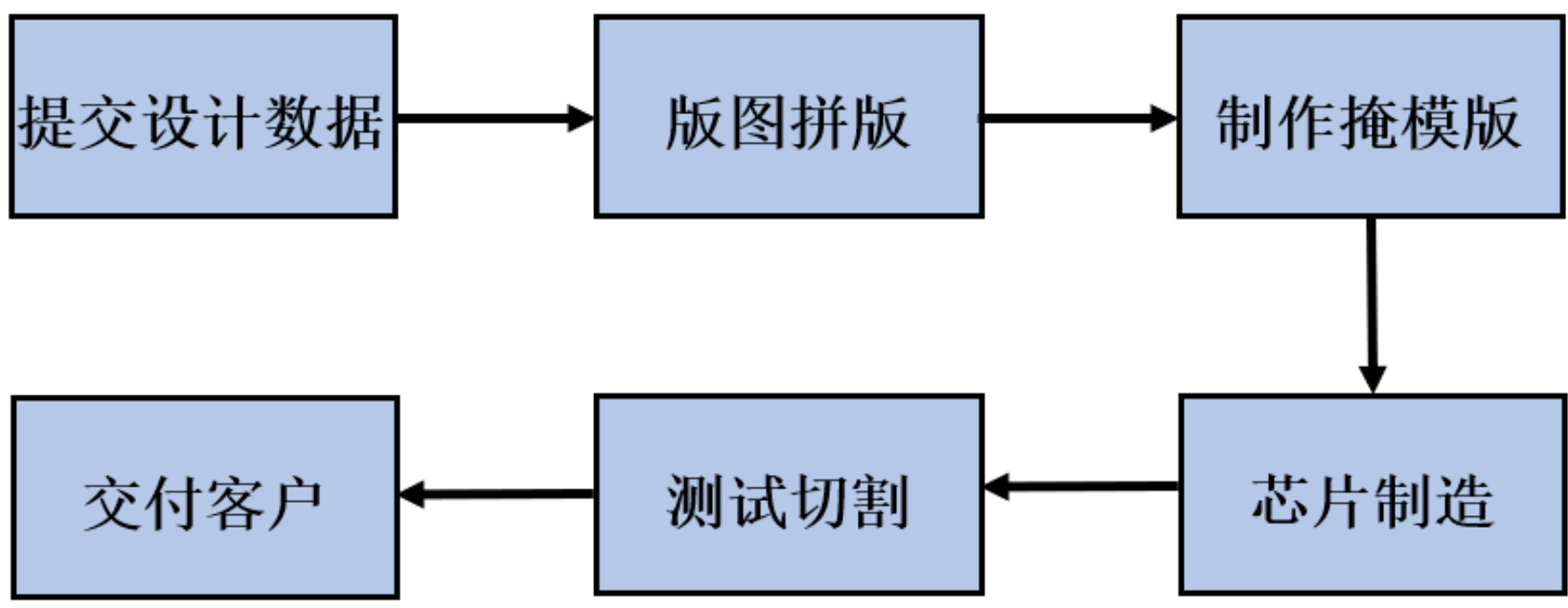

MPW服务流程

WAT

Wafer Acceptance Test

晶圆可接受测试

在晶圆生产出来后,在Fab里要经过WAT测试。WAT对切割道上专门的Test Key进行测试,通过电性参数来监控各道工艺的完成质量和工艺参数的稳定性。WAT测试是出厂前的初选,将有严重生产问题从而电性超出规格之外的wafer筛选出来。